# Simulink<sup>®</sup> HDL Coder™ <u>Release Notes</u>

#### **How to Contact MathWorks**

(a)

www.mathworks.comWebcomp.soft-sys.matlabNewsgroupwww.mathworks.com/contact\_TS.htmlTechnical Support

suggest@mathworks.com bugs@mathworks.com doc@mathworks.com service@mathworks.com info@mathworks.com Product enhancement suggestions Bug reports Documentation error reports Order status, license renewals, passcodes Sales, pricing, and general information

508-647-7001 (Fax)

508-647-7000 (Phone)

The MathWorks, Inc. 3 Apple Hill Drive Natick, MA 01760-2098

For contact information about worldwide offices, see the MathWorks Web site.

Simulink<sup>®</sup> HDL Coder<sup>™</sup> Release Notes

© COPYRIGHT 2007–2011 by The MathWorks, Inc.

The software described in this document is furnished under a license agreement. The software may be used or copied only under the terms of the license agreement. No part of this manual may be photocopied or reproduced in any form without prior written consent from The MathWorks, Inc.

FEDERAL ACQUISITION: This provision applies to all acquisitions of the Program and Documentation by, for, or through the federal government of the United States. By accepting delivery of the Program or Documentation, the government hereby agrees that this software or documentation qualifies as commercial computer software or commercial computer software documentation as such terms are used or defined in FAR 12.212, DFARS Part 227.72, and DFARS 252.227-7014. Accordingly, the terms and conditions of this Agreement and only those rights specified in this Agreement, shall pertain to and govern the use, modification, reproduction, release, performance, display, and disclosure of the Program and Documentation by the federal government (or other entity acquiring for or through the federal government) and shall supersede any conflicting contractual terms or conditions. If this License fails to meet the government's needs or is inconsistent in any respect with federal procurement law, the government agrees to return the Program and Documentation, unused, to The MathWorks, Inc.

#### Trademarks

MATLAB and Simulink are registered trademarks of The MathWorks, Inc. See www.mathworks.com/trademarks for a list of additional trademarks. Other product or brand names may be trademarks or registered trademarks of their respective holders.

#### Patents

MathWorks products are protected by one or more U.S. patents. Please see www.mathworks.com/patents for more information.

## Contents

| Summary by Version                                                    | 1  |

|-----------------------------------------------------------------------|----|

| Version 2.2 (R2011b) Simulink <sup>®</sup> HDL Coder Software         | 4  |

| Version 2.1 (R2011a) Simulink® HDL Coder Software                     | 8  |

| Version 2.0 (R2010b) Simulink <sup>®</sup> HDL Coder Software         | 18 |

| Version 1.7 (R2010a) Simulink <sup>®</sup> HDL Coder Software         | 33 |

| Version 1.6 (R2009b) Simulink <sup>®</sup> HDL Coder Software         | 41 |

| Version 1.5 (R2009a) Simulink <sup>®</sup> HDL Coder Software         | 52 |

| Compatibility Summary for Simulink <sup>®</sup> HDL Coder<br>Software | 64 |

## **Summary by Version**

This table provides quick access to what's new in each version. For clarification, see "Using Release Notes" on page 1.

| Version (Release)               | New Features and<br>Changes | Version<br>Compatibility<br>Considerations | Fixed Bugs and<br>Known Problems |

|---------------------------------|-----------------------------|--------------------------------------------|----------------------------------|

| Latest Version<br>V2.2 (R2011b) | Yes<br>Details              | None                                       | Bug Reports                      |

| V2.1 (R2011a)                   | Yes<br>Details              | None                                       | Bug Reports                      |

| V2.0 (R2010b)                   | Yes<br>Details              | Yes<br>Summary                             | Bug Reports                      |

| V1.7 (R2010a)                   | Yes<br>Details              | Yes<br>Summary                             | Bug Reports                      |

| V1.6 (R2009b)                   | Yes<br>Details              | Yes<br>Summary                             | None                             |

| V1.5 (R2009a)                   | Yes<br>Details              | Yes<br>Summary                             | None                             |

### **Using Release Notes**

Use release notes when upgrading to a newer version to learn about:

- New features

- Changes

- Potential impact on your existing files and practices

Review the release notes for other MathWorks<sup>®</sup> products required for this product (for example, MATLAB<sup>®</sup> or Simulink<sup>®</sup>). Determine if enhancements, bugs, or compatibility considerations in other products impact you.

If you are upgrading from a software version other than the most recent one, review the current release notes and all interim versions. For example, when you upgrade from V1.0 to V1.2, review the release notes for V1.1 and V1.2.

### What Is in the Release Notes

#### **New Features and Changes**

- New functionality

- Changes to existing functionality

#### **Version Compatibility Considerations**

When a new feature or change introduces a reported incompatibility between versions, the **Compatibility Considerations** subsection explains the impact.

Compatibility issues reported after the product release appear under Bug Reports at the MathWorks Web site. Bug fixes can sometimes result in incompatibilities, so review the fixed bugs in Bug Reports for any compatibility impact.

#### **Fixed Bugs and Known Problems**

MathWorks offers a user-searchable Bug Reports database so you can view Bug Reports. The development team updates this database at release time and as more information becomes available. Bug Reports include provisions for any known workarounds or file replacements. Information is available for bugs existing in or fixed in Release 14SP2 or later. Information is not available for all bugs in earlier releases.

Access Bug Reports using your MathWorks Account.

### **Documentation on the MathWorks Web Site**

Related documentation is available on mathworks.com for the latest release and for previous releases:

- Latest product documentation

- Archived documentation

### Version 2.2 (R2011b) Simulink HDL Coder Software

This table summarizes what's new in Version 2.2 (R2011b):

| New Features and Changes | Version Compatibility<br>Considerations | Fixed Bugs and Known<br>Problems |

|--------------------------|-----------------------------------------|----------------------------------|

| Yes<br>Details below     | None                                    | Bug Reports                      |

New features and changes introduced in this version are:

- "Black Box Implementation Enables Specification of Library for Loading VHDL Component" on page 4

- "Option to Minimize Intermediate Signals in HDL Code" on page 4

- "Option to Exclude Time/Date Information in HDL File Header" on page 6

### Black Box Implementation Enables Specification of Library for Loading VHDL Component

For black box implementations of subsystems, you can now specify the library from which to load a VHDL component. The following example specifies mylib as the library:

hdlset\_param(gcb, 'VHDLComponentLibrary', 'mylib');

This enhancement enables you to specify a VHDL component library other than work.

For more information, see:

- "Generating a Black Box Interface for a Subsystem"

- "Customizing the Generated Interface"

### **Option to Minimize Intermediate Signals in HDL Code**

R2011b provides an option to minimize intermediate signals:

| 🍓 Configuration Parameters: sfir           | r_fixed/Configuration (Act              | ive)              |                          |                   | × |

|--------------------------------------------|-----------------------------------------|-------------------|--------------------------|-------------------|---|

| Select:                                    | Clock settings                          |                   |                          |                   |   |

| Solver<br>Data Import/Export               | Reset type:                             | Asynchronous -    | Reset asserted level:    | Active-high 🔹     |   |

| Optimization                               | Clock input port:                       | clk               | Clock enable input port: | clk_enable        |   |

| ⊕-Diagnostics                              | Reset input port:                       | reset             | Clock inputs:            | Single 🗸          |   |

| Hardware Implementat<br>Model Referencing  | Oversampling factor:                    | 1                 |                          |                   |   |

| ⊕-Simulation Target                        | Additional settings                     |                   |                          |                   | 5 |

| È-Code Generation<br>⊡-HDL Code Generation | General Ports                           | Advanced          |                          |                   |   |

| Global Settings                            | 🔲 Balance Delays                        |                   |                          |                   |   |

| Test Bench<br>EDA Tool Scripts             | 🔲 Hierarchical Distr                    | ibuted Pipelining |                          |                   | Ξ |

|                                            | Scalarize vector ports                  |                   |                          |                   |   |

|                                            | Represent constant values by aggregates |                   |                          |                   |   |

|                                            | Use "rising_edge" for registers         |                   |                          |                   |   |

|                                            | Coop unrolling                          |                   |                          |                   |   |

|                                            | Cast before sum                         |                   |                          |                   |   |

|                                            | Use Verilog `timescale directives       |                   |                          |                   |   |

|                                            | 👿 Inline VHDL confi                     | guration          |                          |                   |   |

|                                            | 🔽 Concatenate type                      | safe zeros        |                          |                   |   |

|                                            | Emit time/date stamp in header          |                   |                          |                   |   |

|                                            | ☑ Optimize timing controller            |                   |                          |                   |   |

|                                            | Minimize clock enables                  |                   |                          |                   |   |

|                                            | 🔲 Minimize interme                      | diate signals     |                          |                   |   |

|                                            |                                         |                   |                          |                   | Т |

| 0                                          |                                         |                   | ОК                       | Cancel Help Apply | у |

By removing intermediate signals and omitting declarations for those signals, you can enable better code coverage. For new models, this option is off by default. When you open existing models, this option is also off to preserve backward compatibility.

For more information, see MinimizeIntermediateSignals in the Simulink  $^{\circledast}$  HDL Coder  $^{\text{TM}}$  documentation.

# Option to Exclude Time/Date Information in HDL File Header

R2011b provides an option to exclude time/date information in the generated HDL file header:

| 🆏 Configuration Parameters: sfir                               | _fixed/Configuration (Act               | ive)              |                          |                   | 3        |

|----------------------------------------------------------------|-----------------------------------------|-------------------|--------------------------|-------------------|----------|

| Select:                                                        | Clock settings                          |                   |                          |                   | <b>^</b> |

| Solver<br>Data Import/Export                                   | Reset type:                             | Asynchronous 🔹    | Reset asserted level:    | Active-high 🔹     |          |

| ⊕-Optimization                                                 | Clock input port:                       | ck                | Clock enable input port: | clk_enable        |          |

| ⊡ Diagnostics                                                  | Reset input port:                       | reset             | Clock inputs:            | Single 🔹          |          |

| Hardware Implementat                                           | Oversampling factor:                    | 1                 |                          |                   |          |

| ™Model Referencing<br>⊡~Simulation Target<br>⊡~Code Generation | Additional settings                     |                   |                          |                   |          |

| E-HDL Code Generation                                          | General Ports                           | Advanced          |                          |                   |          |

| Global Settings                                                | 🔲 Balance Delays                        |                   |                          |                   |          |

| Test Bench<br>EDA Tool Scripts                                 | 📃 Hierarchical Distr                    | ibuted Pipelining |                          |                   | Ε        |

| EDA 1001 Scripts                                               | 📃 🔲 Scalarize vector p                  | oorts             |                          |                   |          |

|                                                                | Represent constant values by aggregates |                   |                          |                   |          |

|                                                                | Use "rising_edge" for registers         |                   |                          |                   |          |

|                                                                | 🔲 Loop unrolling                        |                   |                          |                   |          |

|                                                                | ✓ Cast before sum                       |                   |                          |                   |          |

|                                                                | Use Verilog `timescale directives       |                   |                          |                   |          |

|                                                                | 📝 Inline VHDL confi                     | guration          |                          |                   |          |

|                                                                | 🔽 Concatenate type                      | safe zeros        |                          |                   |          |

|                                                                | Emit time/date stamp in header          |                   |                          |                   |          |

|                                                                | Optimize timing controller              |                   |                          |                   |          |

|                                                                |                                         |                   |                          |                   |          |

|                                                                | 🔲 Minimize interme                      |                   |                          |                   |          |

|                                                                |                                         |                   |                          |                   | -        |

| •                                                              |                                         | III               |                          | 4                 |          |

| 0                                                              |                                         |                   | ОК                       | Cancel Help Apply |          |

By excluding the time/date information in the file header, you can more easily determine if two HDL files contain identical code. You can also avoid extraneous revisions of the same file when checking in HDL files to a source code management (SCM) system. For new models, this option is on by default. When you open existing models, this option is also on to preserve backward compatibility.

For more information, see DateComment in the Simulink HDL Coder documentation.

### Version 2.1 (R2011a) Simulink HDL Coder Software

This table summarizes what's new in Version 2.1 (R2011a):

| New Features and Changes | Version Compatibility<br>Considerations | Fixed Bugs and Known<br>Problems |

|--------------------------|-----------------------------------------|----------------------------------|

| Yes<br>Details below     | None                                    | Bug Reports                      |

New features and changes introduced in this version are:

- "Synchronous Multiclock Code Generation" on page 8

- "GUI Support for Scalarize Vector Ports Option for VHDL" on page 9

- "GUI Support for Balancing Delays" on page 11

- "Delay Balancing Support for Filter and High-Level Blockset Blocks" on page 12

- "Enhanced CORDIC Algorithm Support" on page 12

- "Enhanced Retiming Features" on page 12

- "Enhanced Resource Sharing" on page 13

- "Enhanced Resource Utilization Report" on page 13

- "Enhanced Synthesis Script Generation" on page 13

- "Generic Parameter Passing to Subsystems With BlackBox Interface" on page 15

- "HDL Workflow Advisor Integrated FPGA Development Workflow" on page 16

- "Viterbi Decoder Enhancements" on page 16

- "Support for From and Goto Blocks at Any Level in Model" on page 17

### Synchronous Multiclock Code Generation

Release R2011a now supports synchronous multiple clock code generation. You can specify multiple clocks in one of the following ways:

- Use the new property ClockInputs with the function makehdl and specify value as 'Multiple'.

- In the Global Settings Clock settings pane, select 'Multiple' for the Clock inputs field.

When using single clock mode, HDL code generated from multirate models employs a single master clock that corresponds to the base rate of the DUT. When using multiple clock mode, HDL code generated from multirate models employs one clock input for each rate in the DUT. The number of timing controllers generated in multiple clock mode depends on the design in the DUT.

The new property supports values 'Single' and 'Multiple', and defaults to 'Single'. In this mode, the tool's behavior is unchanged from the current behavior.

## GUI Support for Scalarize Vector Ports Option for VHDL

The Scalarize Vector Ports option provides GUI support for the ScalarizePorts property. Scalarize Vector Ports is located in the Advanced pane of the Global Settings section of the Configuration Parameters dialog, as shown in the following figure.

| 🖏 Configuration Parameters: rcosflt_                | tb/Configuration (Active)               |                  |                          |                 | x          |

|-----------------------------------------------------|-----------------------------------------|------------------|--------------------------|-----------------|------------|

| Select:                                             | Clock settings                          |                  |                          |                 | - <b>^</b> |

| -Solver                                             | Reset type:                             | Asynchronous 🔹   | Reset asserted level:    | Active-high 🗸   | ]          |

| Data Import/Export<br>Optimization                  | Clock input port:                       | clk              | Clock enable input port: | clk_enable      |            |

| ⊕-Diagnostics                                       | Reset input port:                       | reset            | Clock inputs:            | Single -        |            |

| Hardware Implementation<br>Model Referencing        | Oversampling factor:                    | 1                |                          |                 |            |

| È-Simulation Target<br>È-Code Generation<br>⊡Report | Additional settings                     | Advanced         |                          |                 |            |

| Comments                                            | 🔲 Balance Delays                        |                  |                          |                 |            |

| Symbols<br>Custom Code                              | 🔲 Hierarchical Distr                    | buted Pipelining |                          |                 | Ε          |

| Debug                                               | 📃 🔲 Scalarize vector p                  | ports            |                          |                 |            |

| Interface                                           | Represent constant values by aggregates |                  |                          |                 |            |

| ⊡-HDL Code Generation<br>Global Settings            | Use "rising_edge" for registers         |                  |                          |                 |            |

| Test Bench                                          | 🗖 Loop unrolling                        |                  |                          |                 |            |

| EDA Tool Scripts                                    | Cast before sum                         |                  |                          |                 |            |

|                                                     | Use Verilog `timescale directives       |                  |                          |                 |            |

|                                                     | 📝 Inline VHDL config                    | guration         |                          |                 |            |

|                                                     | 🛛 🗹 Concatenate type                    | safe zeros       |                          |                 |            |

|                                                     | Emit time/date stamp in header          |                  |                          |                 |            |

|                                                     |                                         |                  |                          |                 |            |

|                                                     | Minimize clock enables                  |                  |                          |                 |            |

|                                                     | 📃 Minimize interme                      | diate signals    |                          |                 |            |

|                                                     |                                         |                  |                          |                 | ÷          |

| <b>@</b>                                            |                                         |                  | OK                       | Cancel Help App | ly         |

**Scalarize Vector Ports** lets you control how the coder generates VHDL code for vector ports. When you select **Scalarize Vector Ports**, the coder flattens each vector port into a structure of scalar ports.

This option is enabled when the selected  ${\bf Language}$  for code generation is VDHL.

See ScalarizePorts in the Simulink HDL Coder documentation for details.

### **GUI Support for Balancing Delays**

The **Balance Delays** option provides GUI support for the **BalanceDelays** property. **Balance Delays** is located in the **Advanced** pane of the **Global Settings** section of the Configuration Parameters dialog, as shown in the following figure.

| 🍓 Configuration Parameters: rcosflt | _tb/Configuration (Active)        |                                         |                          |             | 8        |

|-------------------------------------|-----------------------------------|-----------------------------------------|--------------------------|-------------|----------|

| Select:                             | Clock settings                    |                                         |                          |             | ^        |

| Solver                              | Reset type:                       | Asynchronous -                          | Reset asserted level:    | Active-high | -        |

| Data Import/Export                  | Clock input port:                 | clk                                     | Clock enable input port: | clk enable  | =        |

| ⊕-Optimization<br>⊕-Diagnostics     |                                   |                                         |                          | _           |          |

| -Hardware Implementation            | Reset input port:                 | reset                                   | Clock inputs:            | Single      | _        |

| -Model Referencing                  | Oversampling factor:              | 1                                       |                          |             |          |

| ⊕-Simulation Target                 | Additional settings               |                                         |                          |             |          |

| E-Code Generation                   |                                   | Adversed                                |                          |             |          |

| Report<br>Comments                  | General Ports                     | Advanced                                |                          |             |          |

| Symbols                             | 🔲 Balance Delays                  |                                         |                          |             |          |

| Custom Code                         | 📃 Hierarchical Distr              | ibuted Pipelining                       |                          |             | E        |

| Debug                               | 📃 Scalarize vector p              | ports                                   |                          |             |          |

| Interface                           | 📃 Represent consta                | Represent constant values by aggregates |                          |             |          |

| É-HDL Code Generation               | Use "rising_edge" for registers   |                                         |                          |             |          |

| Global Settings<br>Test Bench       |                                   |                                         |                          |             |          |

| -EDA Tool Scripts                   | Cast before sum                   |                                         |                          |             |          |

|                                     |                                   |                                         |                          |             |          |

|                                     | Use Verilog `timescale directives |                                         |                          |             |          |

|                                     | 🔽 Inline VHDL config              | guration                                |                          |             |          |

|                                     | 🔽 Concatenate type                | safe zeros                              |                          |             |          |

|                                     | 📝 Emit time/date st               | amp in header                           |                          |             |          |

|                                     | ☑ Optimize timing controller      |                                         |                          |             |          |

|                                     | Minimize clock enables            |                                         |                          |             |          |

|                                     | 📃 Minimize interme                | diate signals                           |                          |             |          |

|                                     |                                   |                                         |                          |             |          |

|                                     |                                   |                                         |                          |             | <b>▼</b> |

|                                     |                                   |                                         | OK                       | Cancel Help | Apply    |

When you select **Balance Delays**, if the coder detects the introduction of new delays along one path, it ensures that matching delays are inserted on all other paths. See "Delay Balancing" in the Simulink HDL Coder documentation for details.

### Delay Balancing Support for Filter and High-Level Blockset Blocks

Added delay balancing support for filter and high-level blockset blocks. This addition removes a limitation in this feature from an earlier release. See "Delay Balancing" in the Simulink HDL Coder documentation.

### **Enhanced CORDIC Algorithm Support**

Simulink HDL Coder now adds HDL code generation support for:

- The cos+jsin (complex exponential) function of the Trigonometric Function block, using the CORDIC approximation

- The CORDIC approximation method of the Magnitude-Angle to Complex block

- Use of unsigned data types with CORDIC approximation methods for sin and cos functions

- The cordicrotate function of the MATLAB Function block

See also "Trigonometric Function Block Requirements and Restrictions" in the Simulink HDL Coder documentation.

### **Enhanced Retiming Features**

R2011a enhancements to Distributed Pipelining allow retiming to be applied across a subsystem hierarchy.

- New global parameter HierarchicalDistPipelining, which is set to off by default.

- SLHC applies retiming hierarchically down until DistributedPipelining is turned off for a given subsystem.

- If HierarchicalDistPipelining is turned off, it resorts to the old functionality, i.e., distribution only happens within a subsystem.

- If you turn on the OptimizationReport property, the tool adopts an enhanced reporting mechanism to provide the following:

- If 'HierarchicalDistPipelining' is on, it shows the distributed pipelining report, region-wise.

• If the distributed pipelining fails, it gives some information that might help you correct the failure mode.

### **Enhanced Resource Sharing**

R2011a resource sharing is enhanced as follows:

- Previously, atomic subsystems could be used in data-dependent sharing only if they did not contain any state elements. The removal of this restriction allows sharing in designs like IIR filters

- Previously, the coder did not allow blocks contained in any feedback loop to be shared. In R2011a, you can share blocks within a feedback loop, provided that there are sufficient delays (Unit Delays or Integer Delays) available within the feedback loop to enable semantics-preserving resource sharing.

To construct a sharable feedback loop, connect a Unit Delay or Integer Delay to the output of all Gain and Product blocks within the loop.

See also "Streaming, Resource Sharing, and Delay Balancing" in the Simulink HDL Coder documentation.

### **Enhanced Resource Utilization Report**

The Resource Utilization Report now provides information on additional resources:

- Multiplexers (MUXes), including number and bit width of MUXes

- RAMs. including number of RAMs and their depth and bit width.

### **Enhanced Synthesis Script Generation**

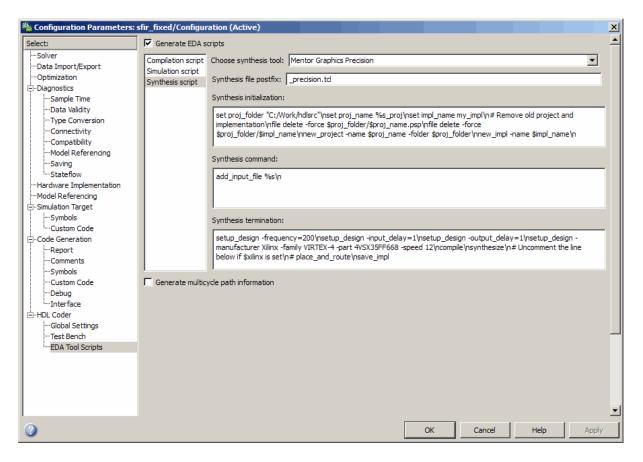

R2011a lets you generate synthesis scripts specifically designed for your choice of one of the following synthesis tools:

- Xilinx<sup>®</sup> ISE

- Mentor Graphics<sup>®</sup> Precision

- Altera<sup>®</sup> Quartus II

- Synopsys<sup>®</sup>Synplify Pro<sup>®</sup>

You can select a synthesis tool in either of the following ways:

- In the **EDA Tool Scripts** pane of the Configuration Parameters dialog box, pick a synthesis tool from the **Choose synthesis tool** pulldown menu.

- In a makehdl command, set the value of the new 'HDLSynthTool' property.

When you select a synthesis tool, the coder:

- Enables synthesis script generation.

- Enters a file name postfix (specific to the chosen synthesis tool) into the **Synthesis file postfix** field.

- Enters strings (specific to the chosen synthesis tool) into the initialization, command, and termination fields.

The following figure shows the **Synthesis script** pane, with default option values entered for the Mentor Graphics Precision tool.

See also "Synthesis Script Options" in the Simulink HDL Coder documentation.

## Generic Parameter Passing to Subsystems With BlackBox Interface

The BlackBox implementation for subsystems now includes the 'GenericList' implementation parameter. Using 'GenericList', you can pass a list of parameter/value pairs (with optional data type specification) in string format to any subsystem having a BlackBox implementation. You specify 'GenericList' as a cell array of string data. Each element of the cell array is another cell array, of the form {'Name', 'Value', 'Type'}.'Type' is optional. If you omit 'Type', 'integer' is passed as the data type.

The following example specifies two generic parameters, named 'Width' and 'CntToNum', to be passed to the BlackBox interface generated for the current subsystem. The data type for 'Width' is specified. The data type for 'CntToNum' is not specified.

```

hdlset_param(gcb, 'GenericList', '{{''Width'', ''8'', ''integer''}, {''

```

#### HDL Workflow Advisor Integrated FPGA Development Workflow

In R2011a, the HDL Workflow Advisor supports an FPGA development workflow that integrates the following tasks:

- Set Target Device and Synthesis Tool: Selection of a target FPGA development board and supporting synthesis tool. A large number of development boards are now supported.

- Set Target Interface: Specification of I/O interface for the target board

- **Download to Target**, **Program Target Device**: Synthesis of generated HDL code and programming of the target board

- Generate xPC Interface: Generate xPC Target interface subsystem, which automatically creates an interface between the xPC Target<sup>™</sup> system and Speedgoat FPGA boards.

For more information, see "Automated Workflows for Specific Target Devices and Synthesis Tools".

### Viterbi Decoder Enhancements

The Viterbi decoder now supports RAM-based traceback for HDL code generation.

# Support for From and Goto Blocks at Any Level in Model

In previous releases, the coder supported From and Goto blocks only if the connected blocks were located at the same subsystem level.

In R2011a, the coder supports use of From and Goto blocks at any level in the model hierarchy inside of the DUT.

### Version 2.0 (R2010b) Simulink HDL Coder Software

This table summarizes what's new in Version 2.0 (R2010b):

| New Features and Changes | Version Compatibility<br>Considerations                                                               | Fixed Bugs and Known<br>Problems |

|--------------------------|-------------------------------------------------------------------------------------------------------|----------------------------------|

| Yes<br>Details below     | Yes—Details labeled<br>as <b>Compatibility</b><br><b>Considerations</b> , below.<br>See also Summary. | Bug Reports                      |

New features and changes introduced in this version are:

- "HDL Parameters Now Saved to Model, Eliminating Need For Control Files" on page 19

- "Additional Simulink Blocks Supported for HDL Code Generation" on page 22

- "Resource Streaming and Sharing Optimizations Conserve Chip Area" on page 23

- "Delay Balancing" on page 24

- "New Timing Controller Naming Convention Avoids Name Clashes" on page 25

- "Scalarized Ports Option for VHDL" on page 25

- "Pipelining Improvements for Filter Blocks" on page 26

- "Reusable Code Generation for Atomic Subsystems" on page 27

- "Resource Utilization and and Optimization Reports" on page 28

- "Limitation on Generated Verilog Black Box Interfaces Removed" on page 31

- "Model Blocks Within Enabled and Triggered Subsystems Supported" on page 32

- "InitializeBlockRAM Property Controls Generation of Initial Signal Values for RAMs" on page 32

- "AddClockEnablePort Implementation Parameter for RAM Blocks Removed" on page 32

- "Do Not Use Floor Rounding Mode for Signed Integer Division" on page 32

### HDL Parameters Now Saved to Model, Eliminating Need For Control Files

In R2010b, the coder saves all non-default HDL-related model settings, block implementation selections and implementation parameter settings to the model file. This eliminates the need to maintain a separate control file. Because the coder saves only the non-default parameter settings, the loading and saving of models is more efficient.

As of release R2010b, the coder does not support the attachment of a control file to a new model. If you have existing models with attached control files, you should convert them to the current format and remove control file linkage. The "Compatibility Considerations" on page 22 section of this release note describes this simple process.

In R2010b, the coder provides both GUI enhancements and utility functions that let you select block implementations, set HDL-related model and block parameters, and perform other functions that previously required control files. "Setting HDL Block Properties in the GUI" on page 19 and "Setting and Getting HDL Block and Model Properties Programatically" on page 21 summarize these enhancements.

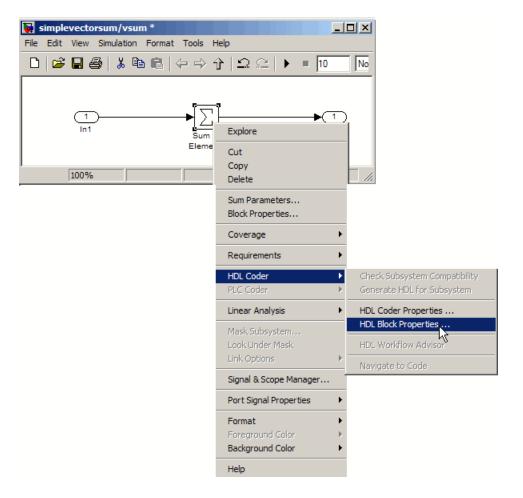

#### Setting HDL Block Properties in the GUI

R2010b lets you select block implementations and set implementation parameters using the new **HDL Properties** dialog box. This dialog box is available via the **HDL Coder** block context menu. The following figure shows this menu when accessed from a Sum of Elements block.

When you select **HDL Block Properties**, the **HDL Properties** dialog box for the block opens. The following figure shows the dialog box for a Sum of Elements block. The **Implementation** section of the dialog box lets you select one of three block implementations. The **Implementation Parameters** section of the dialog box and lets you view and set implementation parameters. For this block, all implementations support the **InputPipeline** and **OutputPipeline** parameters.

| HDL Properties: Sum of     | Elements X        |

|----------------------------|-------------------|

| -Implementation            |                   |

| Architecture               | Linear            |

| J                          | Cascade           |

| -Implementation Parameters |                   |

| InputPipeline              | Tree<br>0         |

| OutputPipeline             | 0                 |

|                            |                   |

| ОК                         | Cancel Help Apply |

For further information, see "Selecting Block Implementations and Setting Implementation Parameters with the HDL Block Properties Dialog Box" in the Simulink HDL Coder documentation.

## Setting and Getting HDL Block and Model Properties Programatically

The following new functions provided by R2010b let you report or set HDL-related property values at the block and model levels:

- hdlset\_param: Set HDL-related parameters at the model or block level.

- hdlget\_param: Return the value of specified HDL block-level parameter (or of all parameters) for a specified block.

- hdldispblkparams: Display HDL-related block parameters that have nondefault values, or all HDL-related block parameters for a specified block.

- hdldispmdlparams: Display HDL-related model parameters that have nondefault values, or all HDL-related model parameters.

- hdlapplycontrolfile: Apply settings from a control file to a model or subsystem.

See also "Specifying Block Implementations and Parameters for HDL Code Generation" in the Simulink HDL Coder documentation:

#### **Compatibility Considerations**

For backward compatibility, the coder continues to support code generation for existing models that have attached control files. The recommended practice is to convert such models to the current format and remove control file linkage.

To convert a model that has an attached control file:

**1** Open the model. When the coder opens a model that has an attached control file, it loads and sets parameters as specified in the control file, and clears the control file linkage from the model. During this process, the coder displays the following messages:

Found HDL control file attached to the model 'test\_model' ... Loading control file 'test\_model\_control' ... Successfully loaded control file 'test\_model\_control.m' ... Please consider saving the model to make changes permanent ... Detaching the HDL control file from the model...

**2** Save the model. The model now preserves all non-default settings. The next time you open the model, the coder will not display any control file status messages.

## Additional Simulink Blocks Supported for HDL Code Generation

The coder now supports the blocks listed in the following table for HDL code generation.

"Summary of Block Implementations" in the Simulink HDL Coder documentation gives a complete listing of blocks that the coder supports for HDL code generation.

| Block                                                                                 | Notes                                                                            |

|---------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

| hdldemolib/HDL FIFO                                                                   | This block implements a first-in<br>first-out (FIFO) register. See "HDL<br>FIFO" |

| Communications System Toolbox™/Channel<br>Coding/Convolutional /Convolutional Encoder | See "Convolutional Encoder Block<br>Requirements and Restrictions"               |

| Block                                                                                                                                              | Notes                                                                                                                                                                      |

|----------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Communications System Toolbox/Digital Baseband<br>Modulation/AM:<br>• Rectangular QAM Demodulator Baseband<br>• Rectangular QAM Modulator Baseband | See "Rectangular QAM Demodulator<br>Baseband Block Requirements and<br>Restrictions"<br>See "Rectangular QAM Modulator<br>Baseband Block Requirements and<br>Restrictions" |

| Communications System<br>Toolbox/Interleaving/Convolutional:<br>• Convolutional Deinterleaver<br>• Convolutional Interleaver                       | Release 2010b adds RAM-based<br>implementations for these blocks.<br>See "Convolutional Interleaver and<br>Deinterleaver Block Requirements<br>and Restrictions"           |

| Communications System<br>Toolbox/Interleaving/Convolutional:<br>• General Multiplexed Deinterleaver<br>• General Multiplexed Interleaver           | See "General Multiplexed<br>Interleaver and Deinterleaver Block<br>Requirements and Restrictions"                                                                          |

### Resource Streaming and Sharing Optimizations Conserve Chip Area

R2010b introduces two related techniques that help you to conserve hardware resources and chip area:

*Streaming* is an optimization in which the coder transforms a vector data path to a scalar data path (or to several smaller-sized vector data paths) that executes at a faster rate. The generated code saves chip area by multiplexing the data over a smaller number of hardware resources. In effect, streaming allows some number of computations to share a hardware resource.

*Resource sharing* is an optimization in which the coder identifies multiple functionally equivalent resources and shares a single resource among them to perform their operations. This technique can realize a substantial reduction in chip area. For example, the generated code may use only one multiplier to perform the operations of several identically-configured multipliers from the original model. The coder achieves this by multiplexing the shared data over the shared resource.

The coder applies streaming and sharing at the subsystem level. You request streaming or sharing by specifying the subsystem HDL parameters StreamingFactor or SharingFactor. You can set these properties in the HDL Properties dialog for a subsystem, as shown in the following figure.

| HDL Properties: Controller |        |  |  |  |  |

|----------------------------|--------|--|--|--|--|

| Implementation             |        |  |  |  |  |

| Architecture               | Module |  |  |  |  |

| Implementation Parameters  |        |  |  |  |  |

| DistributedPipelining      | off    |  |  |  |  |

| InputPipeline              | 0      |  |  |  |  |

| OutputPipeline             | 0      |  |  |  |  |

| SharingFactor              | 0      |  |  |  |  |

| StreamingFactor            | 24     |  |  |  |  |

| OK Cancel Help Apply       |        |  |  |  |  |

See "Streaming, Resource Sharing, and Delay Balancing" in the Simulink HDL Coder documentation for details.

### **Delay Balancing**

In R2010b, the coder supports *delay balancing*, an option that corrects problems that occur when optimizations introduce delays along one path in a model, but equivalent delays are not introduced on other, parallel signal

paths. When you enable delay balancing, if the coder detects introduction of new delays along one path, it ensures that matching delays are inserted on all other paths. When delay balancing is enabled, the coder guarantees that the generated model is functionally equivalent to the original model.

See "Delay Balancing" in the Simulink HDL Coder documentation for details.

# New Timing Controller Naming Convention Avoids Name Clashes

The coder generates a timing controller code file if required by the design, for example when generating code for a multirate model.

In previous releases the timing controller file was always named Timing\_Controller.vhd or Timing\_Controller.v. This naming convention could cause name clashes between timing controllers generated in separate makehdl runs from models within a Model Reference block.

Release 2010b avoids such naming clashes by using a new naming convention for timing controllers, as follows:

- The coder supports a new string property, TimingControllerPostfix. The default value for TimingControllerPostfix is '\_tc'.

- The timing controller name derives from the name of the subsystem that is selected for code generation (the DUT) as DUTname+TimingControllerPostfix.

For example, if the name of the DUT is 'symmetric\_fir', the default name for the associated timing controller would be 'symmetric\_fir\_tc'.

See also TimingControllerPostfix in the Simulink HDL Coder documentation.

### **Scalarized Ports Option for VHDL**

The new ScalarizePorts property for makehdl lets you control how the coder generates VHDL code for vector ports.

When you set ScalarizePorts to 'on', the coder flattens each vector port into a structure of scalar ports.

You can use ScalarizePorts to generate non-conficting port definitions ScalarizePorts if you encounter typing or naming conflicts between vector ports when interfacing two or more generated VHDL code modules.

See ScalarizePorts in the Simulink HDL Coder documentation for details.

### **Pipelining Improvements for Filter Blocks**

In R2010b, three new implementation parameters for filter blocks provide improved pipelining support. The new implementation parameters are:

- AddPipelineRegisters (Default: off): Inserts a pipeline register between stages of computation in a filter.

- MultiplierInputPipeline (Default: 0): Generates a specified number of pipeline stages at multiplier inputs for FIR filter structures.

- MultiplierOutputPipeline (Default: 0): Generates a specified number of pipeline stages at multiplier outputs for FIR filter structures.

The following figure shows these parameters, set to their default values, in the HDL Block Properties dialog box for a Digital Filter block.

| HDL Properties: Digital Filter |                     |  |  |  |  |  |

|--------------------------------|---------------------|--|--|--|--|--|

| -Implementation                |                     |  |  |  |  |  |

| Architecture                   | default             |  |  |  |  |  |

| -Implementation Parameters     |                     |  |  |  |  |  |

| AddPipelineRegisters           | off                 |  |  |  |  |  |

| CoeffMultipliers               | multiplier          |  |  |  |  |  |

| DALUTPartition                 | -1                  |  |  |  |  |  |

| DARadix                        | 2                   |  |  |  |  |  |

| InputPipeline                  | 0                   |  |  |  |  |  |

| MultiplierInputPipeline        | 0                   |  |  |  |  |  |

| MultiplierOutputPipeline       | 0                   |  |  |  |  |  |

| OutputPipeline                 | 0                   |  |  |  |  |  |

| ReuseAccum                     | off                 |  |  |  |  |  |

| SerialPartition                | -1                  |  |  |  |  |  |

| 0                              | K Cancel Help Apply |  |  |  |  |  |

See "Pipelining Implementation Parameters for Filter Blocks" in the Simulink HDL Coder documentation for details.

### **Reusable Code Generation for Atomic Subsystems**

The new HandleAtomicSubsystem property for makehdl lets you generate reusable code for atomic subsystems that are identical. By generating reusable code, you can often eliminate the creation of numerous redundant source code files generated for identical subsystems. HandleAtomicSubsystem is enabled by default.

See "Generating Reusable Code for Atomic Subsystems" in the Simulink HDL Coder documentation for details.

### **Resource Utilization and and Optimization Reports**

The coder now supports generation of two additional report sections to the HDL Code Generation report. You can add these sections to your reports by selecting the options highlighted in the following figure.

| Code Generation Report                   |  |

|------------------------------------------|--|

| Generate traceability report             |  |

| ✓ Include requirements in block comments |  |

| Generate resource utilization report     |  |

| Generate optimization report             |  |

When you select **Generate resource utilization report**, the coder adds a Resource Utilization Report section. The Resource Utilization Report summarizes multipliers, adders/subtractors, and registers consumed by the device under test (DUT). It also includes a detailed report on resources used by each subsystem. The detailed report includes (wherever possible) links back to corresponding blocks in your model.

| 🙀 HDL Code Generation Repor                                                                                                |                                                                                                                                        |    |          |

|----------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|----|----------|

| Contents<br>Summary<br>Resource Utilization<br>Report<br>Optimization Report<br>Distributed<br>Pipelining<br>Streaming and | Resource Utilization Report for<br>dct8_fixed<br><b>Summary</b>                                                                        | -  | <u>^</u> |

| Sharing                                                                                                                    | Multipliers                                                                                                                            |    | 13       |

|                                                                                                                            | Adders/Subtractors<br>Registers                                                                                                        |    | 29<br>32 |

|                                                                                                                            | Detailed Report <pre>[Expand all] [Collapse all] Report for Subsystem: OneD_DCT8 Multipliers (13) </pre> [-] 32x8-bit Multiply : 5     |    |          |

|                                                                                                                            | <pre> • Gain14 • Gain1 • Gain2 • Gain8 • Gain15  [+] 32x16-bit Multiply : 4 [+] 32x32-bit Multiply : 4  Adders/Subtractors (29) </pre> |    |          |

|                                                                                                                            | [+] 8x8-bit Adder : 8                                                                                                                  |    | <b></b>  |

|                                                                                                                            |                                                                                                                                        | ОК | Help     |

When you select **Generate optimization report**, the coder adds an Optimization Report section, with two subsections:

**Distributed Pipelining**: this subsection shows details of subsystem-level distributed pipelining (if any subsystems have the DistributedPipelining option enabled). Details include comparative listings of registers and flip-flops before and after applying the distributed pipelining transform.

**Streaming and Sharing**: this subsection shows both summary and detailed information about all subsystems for which sharing or stream is requested.

The following figure shows the distributed pipelining subsection of a typical Optimization Report.

| 🙀 HDL Code Generation Report                                                 |                                                                         |                                                                                   |                               |                    |

|------------------------------------------------------------------------------|-------------------------------------------------------------------------|-----------------------------------------------------------------------------------|-------------------------------|--------------------|

| Contents<br>Summary<br>Resource Utilization<br>Report<br>Optimization Report | Distributed Pipelining Report for dct8_fixed                            |                                                                                   |                               |                    |

| Distributed<br>Pipelining                                                    | Subsystem                                                               | InputPipeline                                                                     | OutputPipeline                |                    |

| Streaming and                                                                | OneD DCT8                                                               | 2                                                                                 | 2                             |                    |

|                                                                              | OutputPipeline: 2<br>Before Distributed<br>Registers<br>32-bit<br>8-bit | Parameters: Distributed <u>I Pipelining</u> : 32 registe Pipelining : 32 register | Count<br>16<br>16             | .: 2;              |

|                                                                              |                                                                         |                                                                                   |                               |                    |

|                                                                              | Registers<br>32-bit                                                     |                                                                                   | Count<br>10                   |                    |

|                                                                              | 8-bit                                                                   |                                                                                   | 15                            |                    |

|                                                                              | 16-bit                                                                  |                                                                                   | 7                             |                    |

|                                                                              | Generated model                                                         | after Distributed Pipelini                                                        | ng: <u>gm dct8 fi</u> .<br>OK | <u>xed</u><br>Help |

See "Creating and Using Code Generation Reports" in the Simulink HDL Coder documentation for further information.

#### Limitation on Generated Verilog Black Box Interfaces Removed

In previous releases, where Verilog was specified as the target language, the coder supported only scalar ports for code generation with the Subsystem

black box implementation (BlackBox). Release R2010b removes this restriction.

The restriction still applies to some other block types. See "Limitation on Generated Verilog Interfaces" in the Simulink HDL Coder documentation for further information.

### Model Blocks Within Enabled and Triggered Subsystems Supported

The coder now supports HDL code generation for Enabled Subsystem and Triggered Subsystem blocks that contain Model blocks.

### InitializeBlockRAM Property Controls Generation of Initial Signal Values for RAMs

The new InitializeBlockRAM property for the makehdl function lets you enable or suppress generation of initial signal values for RAM blocks.

See also InitializeBlockRAM in the Simulink HDL Coder documentation.

## AddClockEnablePort Implementation Parameter for RAM Blocks Removed

The AddClockEnablePort implementation parameter for the Dual Port RAM and Single Port RAM blocks was deprecated in Release 2009b.

In R2010b, the coder no longer supports  $\mathsf{AddClockEnablePort}$  for RAM blocks.

## Do Not Use Floor Rounding Mode for Signed Integer Division

The coder now displays an error message at code generation time if it encounters use of 'floor' rounding mode for signed integer division. The HDL division operator does not support 'floor' rounding mode.

To avoid this error, use 'fix' mode for signed integer division operations, or else change the signed integer division operations to unsigned integer division.

## Version 1.7 (R2010a) Simulink HDL Coder Software

This table summarizes what's new in Version 1.7 (R2010a):

| New Features and Changes | Version Compatibility<br>Considerations                                                               | Fixed Bugs and Known<br>Problems |

|--------------------------|-------------------------------------------------------------------------------------------------------|----------------------------------|

| Yes<br>Details below     | Yes—Details labeled<br>as <b>Compatibility</b><br><b>Considerations</b> , below.<br>See also Summary. | None                             |

New features and changes introduced in this version are:

- "Simplified Syntax for Specification of Block Implementations in Control Files" on page 34

- "HDL Workflow Advisor" on page 35

- "Additional Simulink Blocks Supported for HDL Code Generation" on page 37

- "CORDIC Algorithm Supported for Trigonometric Functions (sin, cos, sincos)" on page 38

- "Option to Minimize Generation of Clock Enables" on page 38

- "VHDLArchitectureName Property Supports Specification of Architecture Name" on page 38

- "VHDLLibraryName Property Supports Specification of Target Library" on page 38

- "Output Pipelining Now Supported for Subsystems" on page 39

- "Distributed Pipelining Now Supported for Subsystems" on page 39

- "CSD and Factored CSD Optimizations for Constant Multiplications" on page 39

- "Enhanced Gain Block Support" on page 39

- "FIR Decimation Filter Supports Distributed Arithmetic Architecture" on page 40

- "Serial, Partly Serial and Cascade Serial Architectures Supported for FIR Filter Implementations" on page 40

- "InstancePostfix Property Allows Specification of Extension to Postfix String" on page 40

## Simplified Syntax for Specification of Block Implementations in Control Files

In R2010a, the coder supports a simplified syntax for specifying block implementations in a control file. The new syntax lets you specify a block implementation using simple keywords, instead of package.class notation. The new implementation keywords are generic, rather than block-specific. This approach lets you use the same keyword to specify implementation types such as Tree, Cascade, or Linear for all blocks that support such implementations. For example, the following control file specifies that the coder uses a cascade implementation for all Sum blocks and all Product blocks in the model.

```

function cfg = controlFile

cfg = hdlnewcontrol(mfilename);

cfg.forEach('*',...

'built-in/Sum', {},...

'built-in/Product', {},...

'Cascade', {});

```

To specify the default implementation for any block, simply use the keyword 'default', as in the following example.

```

function cfg = controlFile

cfg = hdlnewcontrol(mfilename);

cfg.forEach( './Subsystem/MinMax', ...

'built-in/MinMax', {}, ...

```

'default');

Refer to the Simulink HDL Coder documentation for a complete listing of supported blocks and their implementations.

#### **Compatibility Considerations**

In previous releases, control files specified block implementations using package.class syntax. For example, the following control file specifies the cascade implementation for Sum blocks, using package.class syntax.

```

function cfg = controlFile

cfg = hdlnewcontrol(mfilename);

cfg.forEach('*',...

'built-in/Sum', {},...

'hdldefaults.SumCascadeHDLEmission', {});

```

The coder continues to support control files that use package.class syntax. However, we strongly recommend that you convert existing control files to the new syntax. To convert an existing control file:

- Open a model that is linked to the control file.

- Open the Configuration Parameters dialog box and select the **HDL Coder** pane.

- Click **Generate** to generate HDL code for the model. The code generation process updates in-memory information that will be written to your updated control file.

- In the **Code generation control file** subpane, click **Save**. This overwrites the existing control file. The updated control file will use the new syntax.

#### **HDL Workflow Advisor**

The HDL Workflow Advisor is a GUI tool that supports all stages of the FPGA design process, including the following:

- Checking the Simulink model for HDL code generation compatibility

- HDL code and test bench generation

- Synthesis and timing analysis through integration with third-party synthesis tools (r2010a supports Xilinx ISE)

- Back annotation of the Simulink model with critical path and other information obtained during synthesis.

The following figure shows the top-level HDL Workflow Advisor window.

| S Find: ▼ ♣ ♣                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | ID HDL Workflow Advisor - sfir_fixed/symmetric_fir<br>File Edit Run View Help |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HDL Workflow Advisor         B: (i)       1. Prepare Model For HDL Code Generation         B: (i)       3. FPGA Implementation and Analysis    HDL Workflow Advisor facilitates RTL code (HDL/Verlig) and testbench generation from a system or subsystem, performs synthesis tasks by invoking supported 3rd party synthesis tool, and annotates critical path information on the system. Each task performs synthesis tasks by invoking supported 3rd party synthesis tool, and annotates critical path information on the system. Each task performs synthesis tasks by invoking supported 3rd party synthesis tool, and annotates critical path information on the system. Each task performs any desist tasks, but workflow. Advisor provides you with information on how to modify the original model, use different implementations, or use different code generation options to refine and explore the result. The HDL Workflow Advisor ges through three main tasks. Each task addresses one aspect of the workflow. The tasks are re: <ul> <li>I. Prepare Model for HDL Code Generation</li> <li>Check Algebraic Loops</li> <li>Procedure Folder - run in any order<th></th><th></th></li></ul> |                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| I - Prepare Model For HDL Code Generation         B - B         2 - HDL Code Generation         B - B         3 - BFGA Implementation and Analysis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Current system: sfir_fixed/symmetric_fir                                      | HDL Workflow Advisor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| are:       1. Prepare Model for HDL Code Generation         • Check Global Settings       • Check Algebraic Loops         • Check Block Compatibility       • Check Sample Time         • Check Sample Time       • Check Sample Time         • Passed       • Failed         • Passed       • Failed         • Warning       • Group Folder - run in any order         • Procedure Folder - run sequentially       • Running this check triggers an Update Diagram.         • >>>> Trun to Failure " in progress.       • Not Run: 13         Report       Report       Report:         Report:       …'report 337.html         Date/Time:       Not Applicable         Summary:       • Pass: 0       • Fail: 0         • Warning: 0       • Not Run: 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | I. Prepare Model For HDL Code Generation     I. 2. HDL Code Generation        | performs synthesis tasks by invoking supported 3rd party synthesis tool, and annotates critical path information on the<br>system. Each task performs one distinct step of the workflow. The HDL Workflow Advisor provides you with feedback on<br>the results of the task. If the task fails, the HDL Workflow Advisor provides you with information on how to modify the<br>model to complete the tasks. When you complete the tasks, you have a report synthesis result from one of the supported synthesis tools. If the<br>result does not meet your requirement, you may choose to modify the original model, use different implementations, or |